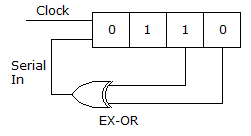

Question

a.

0000

b.

0101

c.

1010

d.

1110

Posted under Electronics and Communication Engineering

Interact with the Community - Share Your Thoughts

Uncertain About the Answer? Seek Clarification Here.

Understand the Explanation? Include it Here.

Q. In following figure, the initial contents of the 4-bit serial in parallel out, right shift, shift register as shown in figure are 0110. After 3 clock pulses the contents of the...

Similar Questions

Explore Relevant Multiple Choice Questions (MCQs)

Q. For the logic circuit of the given figure, the minimized expression is

View solution

Q. The inputs to a NAND gate are as shown in the given figure. The waveform of output is

View solution

Q. In the given figure A = 1, B = 1. B is now changed to a sequence 101010................The outputs X and Y will be

View solution

Q. In 8085 microprocessor, what are the contents of register SP, after the interrupt has been started?

View solution

Q. To have the multiprocessing capabilities of the 8086 microprocessor, the pin connected to the ground is

View solution

Q. A gate in which shift register is connected as shown in the figure below. How many clock pulse (after reset to '0') the contents of the shift register are '000' again?

View solution

Q. For the K map of the given figure the simplified Boolean expression is

View solution

Q. Figure shows three pulse train inputs to a 3-input AND gate. Assuming positive logic, the output signal obtained in figure would be

View solution

Q. A 12-bit binary counter has the following state. The octal number represented is

View solution

Q. For the K map of the given figure the simplified Boolean expression is

View solution

Q. A clock pulse is fed into 3 bit binary down count. The signal at B output is

View solution

Q. The boolean expression for shaded area in the given figure is

View solution

Q. The given figure shows a K-map for a Boolean function. The number of essential prime implicants is

View solution

Q. For the logic circuit given, what is the simplified Boolean function?

View solution

Q. The accuracy of A/D conversion is generally

View solution

Q. Consider the following statements in connection with CMOS inverter in figure where both the MOSFET are of enhancement type and both have a threshold voltage of 2 V

statements 1: T1 conducts when vi ≥ 2 V

statements 2: T1 is always in saturation when v0 = 0 V

Which of the following is correct?

View solution

Q. In number system e.g. 6, a “decade” counter has to recycle to 0 at the sixth count. Which of the connections indicate below will realize this resetting? (a logic “0” at the R inputs resets the counters)

View solution

Q. The logic realized by the circuit shown in figure

View solution

Q. The contents of stack location after the call operation will be

View solution

Q. In figure, R = 20KΩ and C = 75 pF. The converter clock frequency will be

View solution

Recommended Subjects

Are you eager to expand your knowledge beyond Electronics and Communication Engineering? We've handpicked a range of related categories that you might find intriguing.

Click on the categories below to discover a wealth of MCQs and enrich your understanding of various subjects. Happy exploring!